Abstract

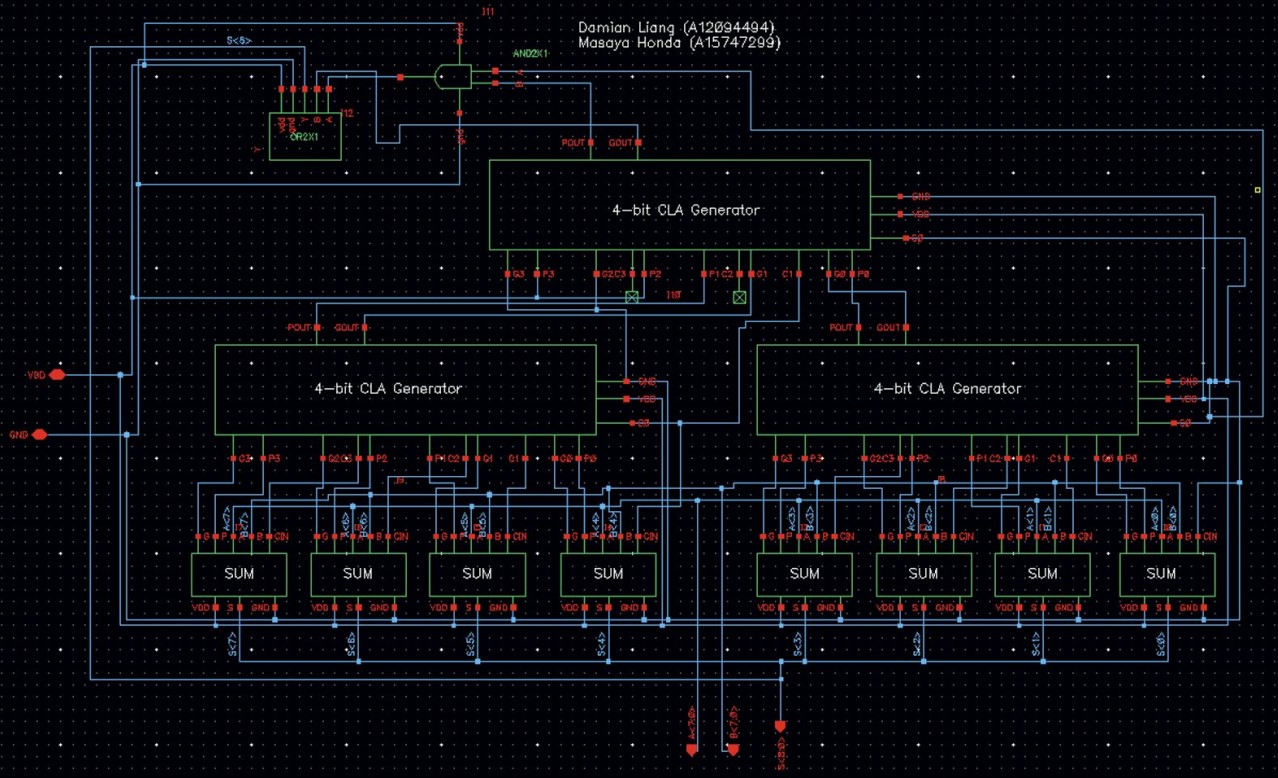

The design challenge of this two-man team project was to create a high-speed transistor level 8-bit hierarchical carry-lookahead adder that is able to achieve a higher performance compared to the ripplecarry adder in Cadence Virtuoso. We implemented the 8-bit carry-lookahead adder by using 4-bit carry-lookahead generator blocks that are responsible for computing the carryout, group propagate, and group generate bits. This architecture also includes the sum block, which computes the sum, propagate, and generate bits based on the inputs and the carry-in. The design process includes hand-designing the schematic, performing partial layout, DRC/LVS checks, and parasitic extractions. The design achieved a maximum clock speed of 6.22GHz pre-extraction and a 4.35GHz post-extraction using a 45nm process.